|

Data type: Стандарты Updated: 22.06.2011 15:07 Протокол обмена процессорных модулей

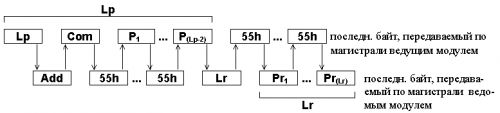

Описание электрических сигналов и логики обмена 1. Основные принципы 1.1. Обмен информацией между процессорными модулями в стандарте интерфейса SCI производится по инициативе и под контролем одного ведущего модуля - контроллера крейта. 1.2. Информация по магистрали передается в параллельном коде 8-ми разрядными байтами в соответствии с требованиями интерфейса SCI. 1.3. Начало обмена по магистрали может инициировать только контроллер крейта. При этом он передает ведомому модулю (адресату) первый байт информации, выполняя на магистрали команду записи по соответствующему адресу. 1.4. При получении любого байта информации адресуемый процессорный модуль должен в течении контрольного времени ( не более 5 мс) поместить в свой буфер обмена байт ответа, при этом он на линии L1 устанавливает сигнал низкого уровня, который фактически является сигналом готовности данных в буфере обмена. 1.5. При управлении пассавными модулями ( безпроцессорными ) контроллер крейта может передавать информацию адресату и получать ее без подтверждения - байт ответа адреатом может не формироваться и, соответсвенно, сигнал запроса на обслуживание не устанавливается. 2. Адресация к ведомым устройствам 2.1. При осуществлении обмена по магистрали SCI применяется упрощенная схема дишефрации адресов, при которой выборка соответствующего модуля (адресата) производится по нулевому уровню одной из линий шины данных в момент прохождения сигнала фиксации адреса ALE. Таким образом в составе одного крейта может работать одновременно не более 8-ми адресуемых устройств. 2.2. Адрес любого устройства должен представлятся байтом, в котором все биты установлены в состоянии логической единицы, за исключением одного разряда по расположению которого и производиться адресная дешифрация. 2.3. Таблица адресов устройств, работающих в стандарте SCI приведена в Приложении 1 (см. ниже). 3. Формат команд и данных Обмен информацией между процессорными модулями в стандарте интерфейса SCI осуществляется в следующем порядке: 3.1. Каждый сеанс обмена информацией (передача одной команды или одного блока данных) начинается с передачи служебного байта команды (см. рисунок 3.1.а), который содержит длину передаваемой посылки. В ответ на служебный байт адресат обязан выдать байт ответа, который содержит физический адрес модуля. При несоответствии адреса принимается решение об ошибке обмена. 3.2. При правильном ответе контроллер следующим байтом передает код команды. В ответ на него адресат должен передать байт подтверждения приема 55Н. 3.3. Передача последующих параметров команды вычисляется аналогично самой команде с получением подтверждения 55H при передаче каждого байта. 3.4. В ответ на передачу последнего параметра команды адресат обязан выдать служебный байт, который содержит длину ответной посылки. 3.5. Для приема ответной посылки контроллер обязан инициировать передачу каждого очередного байта ответа запросом 55H, который адресуется входному модулю. На полученный запрос адресат выдает на шину обмена очередной байт ответной посылки. После передачи адресатом последнего байта обмен считается оконченным.

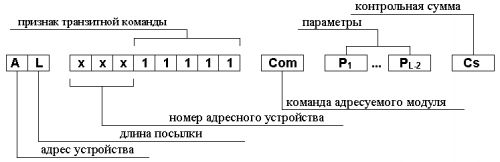

Рис. 1. - Передача служебного байта команды где: Lp - длина передаваемой посылки; 4. Прочие условия (временные характеристики сеанса обмена) 4.1. При приеме очередного байта адресат (ведомый процессорный модуль) обязан выдать байт в ответ в течении тайм-аута, длительность которого определяется техническими особенностями процессорного модуля. 4.2. При отсутствии ответного байта в течении заданного тайм-аута контроллером принимается решение о отсутствии или нарушении обмена (связи). 4.3. При неправильной адресации контроллер обязан повторить запрос по требуемому адресу. Если следующая попытка адресации не окончиться успешно, принимается решение онарушении адресации ведомых процессорных модулей. 5. Организация транзитных команд 5.1. При использовании протокола обмена "ЭХО-1" для передачи команд и данных непосредственно в ведомые модули рекомендуется использовать команды транзитного доступа. Признаком такой команды являются установленные в единицу пять младших битов, т. е. в каждом блоке команд (блок команд типа "принять", "передать" и т. п.) последняя команда определена как команда транзитного доступа. 5.2. Программный драйвер обмена по последовательному порту, получив транзитную команду, удаляет из нее байт-признак транзитной команды и перенаправляет команду модулю, физический адрес которого указан в трех старших битах байта-признака. Таким образом транзитные команды имеют следующий формат:

Рис. 2. - Формат транзитных команд

Приложение 1 ТАБЛИЦА АДРЕСОВ УСТРОЙСТВ, РАБОТАЮЩИХ В СТАНДАРТЕ SCI.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||