|

Data type: Equipment Updated: 15.06.2011 19:04 Контроллер крейта CC02

Контроллер крейта представляет собой двухместный модуль в стандарте КАМАК. Внутри корпуса расположено две печатные платы: плата обработки команд и плата управляющей станции. Сигналы управления от персонального компьютера по соединительному кабелю поступают на плату обработки команд. С помощью микропрограммного автомата преобразуются из последовательного кода в параллельный, и в определенной временной последовательности выводятся на магистраль крейта, а также по внутренней параллельной шине поступают на плату управляющей станции. 1. Плата обработки команд

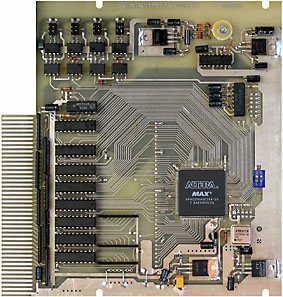

Внешний вид платы обработки команд показан на рисунке 1, а ее принципиальная схема - в Приложении 1.  Рис. 1. - Внешний вид платы обработки команд.

При установке в крейт плата разъемом XS подключается к параллельным проводникам шин данных и управления и контролирует их состояние при выполнении команд управления.

Основой принципиальной схемы платы обработки команд является программируемая логическая матрица MAX EPM3256. Внутренняя прошивка этой микросхемы создает микропрограммный автомат, который состоит из генератора синхросигналов, асинхронного последовательного приемопередатчика, дешифратора команд управления, генератора командного цикла магистрали КАМАК и дешифратора команд магистрали. Сигналы управления TDA, TDB и RXA, RXB через разъем Х1 поступают с магистральной линии связи на согласующие усилители DD3, DD4. После преобразования в ТТЛ-уровни они подаются на оптроны гальванической развязки DD7, DD8 и далее - на входные контакты ПЛМ 133, 136 (сигналы DSR, DRX). В процессе приема управляющей команды или посылки данных происходит сравнение принятого адреса с индивидуальным номером контроллера, который задается с помощью переключателя S1 и вводится в ПЛМ через контакты 119, 120. Если условия приема выполняются, происходит запуск микропрограммного автомата. В зависимости от типа принятой посылки дешифратором команд управления формируется последовательность сигналов, с помощью которых производиться перезапись принятых или прочитанных данных в одну из групп регистров. Если принят нулевой тип команды, то данные с приемника пересылаются на формирователи выходных сигналов ПЛМ (F1..F16, A1..A8, Z, C, IO). При выполнении адресных команд данные разрядов D9..D13, содержащих информацию о номере адресуемого модуля, помещаются на выходы NC1..NC16 и через разъем ХР2 и внутренний шлейф контроллера, соединяющий между собой платы, поступают на плату управляющей станции для дешифрации. После этого происходит запуск командного цикла КАМАК, при выполнении которого формируется предусмотренная стандартом последовательность сигналов В, S1, S2, а также генерируются низкие уровни сигналов EF и EZ, необходимые для открытия магистральных усилителей DD11, DD12 и вывода сигналов управления на магистраль крейта. При выполнении адресных команд активируется также сигнал EN, который на плате управляющей станции разрешает работу дешифратора номера модуля. Во время командного цикла во внутренние триггеры ПЛМ записывается состояние магистральных сигналов X и Q, которые вместе с сигналом I поступают на входные контакты ПЛМ через инверторы микросхемы DD13. Если в командном цикле выполняются команды чтения F(0)..F(7), то одновременно со стробом S1 генерируется низкий логический уровень сигнала S1R, который поступая на входы С регистров DD17, DD18, DD20, приводит к записи в эти регистры информации с шины чтения данных R1..R24. После завершения командного цикла генерируется сигнал RDR, по которому регистры DD17, DD18, DD20 помещают записанные с магистрали данные на внутреннюю шину контроллера DR1..DR24 для загрузки их в передатчик в процессе подготовки ответа. При командах записи F(16)..F(23) на время выполнения командного цикла устанавливается низкий логический уровень сигнала EW, который, поступая на регистры DD15, DD16, DD19, разрешает вывод предварительно записанных в них данных на магистральную шину записи данных W1..W24. Если принят первый тип команды (запрос дополнительных данных с контроллера), то алгоритм дальнейшей работы микропрограммного автомата зависит от содержимого младших трех бит принятой команды. При установленном в единицу бите D0 (флаг RH) вырабатывается низкий логический уровень сигнала RDR, данные из регистров DD17, DD18, DD20 по внутренней шине DR1..DR24 поступают в ПЛМ, где старшие восемь разрядов записываются в передатчик для формирования ответа. Установленный в единицу бит D1 (флаг LL) или бит D2 (флаг LH) приводят к активации сигнала RD-L. Этот сигнал разрешает плате управляющей станции поместить на внутреннюю шину контроллера DR1..DR24 информацию о состоянии магистральной шины прерывания L1..L24. В зависимости от состояния флагов при подготовке передачи ответа в передатчик записываются шестнадцать младших или восемь старших разрядов. Второй тип команды (запись младших шестнадцати разрядов данных) выполняется в следующем порядке. Принятые с канала обмена данные выставляются в параллельном коде на внутреннюю шину DW1..DW16. Генерируется импульс низкого логического уровня на выходе WWL, задним фронтом которого данные записываются в регистры DD15, DD16. Выходы регистров при этом находятся в состоянии высокого сопротивления, и принятые данные на магистраль крейта не поступают. Команда третьего типа (запись старших восьми разрядов данных) выполняется аналогично второму типу, но активируется сигнал WWH, задним фронтом которого восемь старших разрядов с шины DW17..DW24 записываются в регистр DD19. Все сигналы на магистрали крейта в этом цикле остаются пассивными. Обобщенный сигнал запросов на обслуживание L поступает с платы управляющей станции на вход ПЛМ для формирования соответствующего бита в байте состояния контроллера, а также через оптрон DD21 (сигнал LM) и усилитель-формирователь DD5 в виде дифференциаль¬ных сигналов LMA, LMB выводиться на линию связи через разъем Х1. Аналогичным образом с помощью оптрона DD6 и усилителя-формирователя DD2 передается в линию связи сигнал обратной передачи данных DTX. Для питания усилителей-формирователей DD2..DD5 на плате размещен гальванически развязанный источник питания, который обеспечивает эти микросхемы стабилизированным напряжением + 5 В. Источник построен на основе интегрального преобразователя DD1, который запитан от магистрального напряжения питания + 24 В через интегральный стабилизатор DA3 (+ 15 В). Гальваническая развязка обеспечивается трансформатором TR1. С выхода выпрямителя, собранного на диодах VD1..VD4, напряжение поступает на интегральный стабилизатор DA1, и далее - на питание усилителей. Питание ПЛМ осуществляется напряжением + 3,3 В от интегрального стабилизатора DA4, а остальных логических микросхем - напряжением + 5 В от интегрального стабилизатора DA5. Для визуального наблюдения за состоянием магистрали схема содержит ряд светодиодов, которые располагаются на передней панели контроллера. Индикация статических сигналов запрета на магистрали (I) и наличие запросов на обслуживание (L) осуществляется выходными сигналами ПЛМ (I-I, I-L) с помощью светодиодов VL4, VL5. Для индикации кратковременно существующих сигналов B, X и Q применена схема удлинения импульсов, построенная на триггерах микросхемы DD14. Триггеры включены по схеме одновибраторов и нагружены на светодиоды VL1..VL3. Удлинение сигналов обеспечивает их надежную визуальную регистрацию. Для работы микропрограммного автомата, размещенного в ПЛМ, необходима тактовая частота 40 МГц, которую обеспечивает кварцевый генератор DD9. Тактовая частота поступает на вход CLK (контакт 102). Сигнал инициализации ПЛМ при включении напряжения питания вырабатывается супервизором DA2 и поступает на вход RES ПЛМ (контакт 100). Магистральные шины данных и управления подтянуты к источнику питания + 5 В с помощью резисторных сборок R34, R55..R63 для повышения помехозащищенности магистрали. Четырехконтактный разъем JT является технологическим и предназначен для программирования ПЛМ. Вторая плата контроллера - плата станции управления (рис. 2), - предназначена для формирование индивидуальных сигналов выбора номера модуля и первичной обработки запросов на обслуживание, поступающих от модулей. В приложении 2 показана ее принципиальная схема. Рис. 2. - Внешний вид платы станции управления.

Все управляющие сигналы на плату поступают с платы обработки команд через разъем ХР1 по шлейфу межплатных соединений.

Информация о номере выбранного модуля поступает по параллельной шине NC1..NC16 на входы трех дешифраторов DD8..DD10, которые стробируются сигналом EN. Сигнал EN генерируется на плате обработки команд одновременно с сигналом В. Сигналы запросов на обслуживание от модулей крейта логически суммируются с помощью микросхем DD4..DD6 и логического элемента DD7.1. На его выходе низкий уровень сигнала L формируется при наличии хотя бы одного запроса от модулей крейта. Для передачи подробной информации о наличии запросов используются магистральные формирователи DD1..DD3. При появлении низкого уровня сигнала RD-L данные с параллельной шины L1..L23 поступают на параллельную шину DR1..DR23 и далее - на плату обработки команд. Все выходы и входы индивидуальных сигналов шины N и шины L подтянуты к напряжению источника питания + 5 В с помощью резисторных сборок R3..R9 для повышения помехозащищенности магистрали крейта. Микросхемы платы питаются напряжением + 5 В от интегрального стабилизатора DA1, первичное питание которого осуществляется магистральным напряжением + 6 В. |